## MITSUBISHI MICROCOMPUTERS M37221EF-XXXSP,M37221EFSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

#### DESCRIPTION

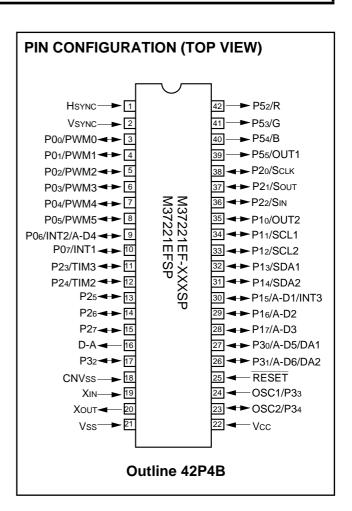

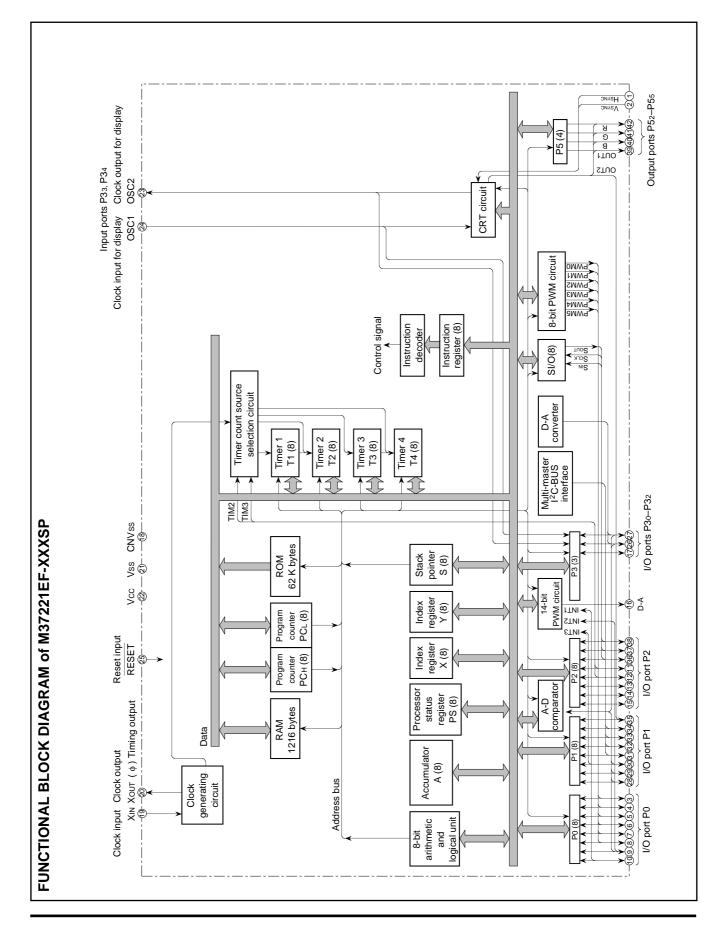

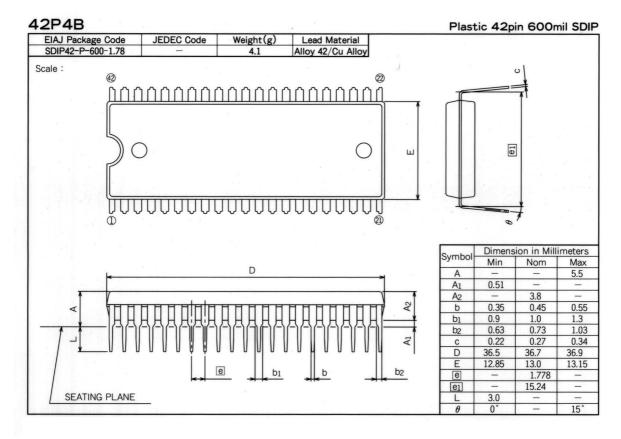

The M37221EF-XXXSP and M37221EFSP are single-chip microcomputers designed with CMOS silicon gate technology. They are housed in a 42-pin shrink plastic molded DIP.

In addition to their simple instruction sets, the ROM, RAM and I/O addresses are placed on the same memory map to enable easy programming.

The M37221EF-XXXSP and M37221EFSP have a PWM output function and a OSD display function, so it is useful for a channel selection system for TV.

#### **FEATURES**

| Number of basic instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory size                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ROM62 K bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RAM 1216 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ROM for display8 K bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RAM for display 96 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The minimum instruction execution time                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0.5 µs (at 8 MHz oscillation frequency)                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power source voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Power dissipation 165 mW                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| (at 8 MHz oscillation frequency, Vcc=5.5V, at CRT display)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Subroutine nesting                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Interrupts 14 types, 14 vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bebit timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8-bit timers         4           Programmable I/O ports (Ports P0, P1, P2, P30–P32)         27           Input ports (Ports P33, P34)         2                                                                                                                                                                                                                                                                                                                                        |

| 8-bit timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8-bit timers         4           Programmable I/O ports (Ports P0, P1, P2, P30–P32)         27           Input ports (Ports P33, P34)         2                                                                                                                                                                                                                                                                                                                                        |

| 8-bit timers         4           Programmable I/O ports (Ports P0, P1, P2, P30–P32)         27           Input ports (Ports P33, P34)         2           Output ports (Ports P52–P55)         4                                                                                                                                                                                                                                                                                       |

| 8-bit timers       4         Programmable I/O ports (Ports P0, P1, P2, P30–P32)       27         Input ports (Ports P33, P34)       2         Output ports (Ports P52–P55)       4         12 V withstand ports       6         LED drive ports       4         Serial I/O       8-bit X 1 channel                                                                                                                                                                                     |

| 8-bit timers       4         Programmable I/O ports (Ports P0, P1, P2, P30–P32)       27         Input ports (Ports P33, P34)       2         Output ports (Ports P52–P55)       4         12 V withstand ports       6         LED drive ports       4         Serial I/O       8-bit X 1 channel         Multi-master I <sup>2</sup> C-BUS interface       1 (2 systems)                                                                                                             |

| 8-bit timers       4         Programmable I/O ports (Ports P0, P1, P2, P30–P32)       27         Input ports (Ports P33, P34)       2         Output ports (Ports P52–P55)       4         12 V withstand ports       6         LED drive ports       4         Serial I/O       8-bit X 1 channel                                                                                                                                                                                     |

| 8-bit timers       4         Programmable I/O ports (Ports P0, P1, P2, P30–P32)       27         Input ports (Ports P33, P34)       2         Output ports (Ports P52–P55)       4         12 V withstand ports       6         LED drive ports       4         Serial I/O       8-bit X 1 channel         Multi-master I <sup>2</sup> C-BUS interface       1 (2 systems)         A-D comparator (6-bit resolution)       6 channels         D-A converter (6-bit resolution)       2 |

| 8-bit timers       4         Programmable I/O ports (Ports P0, P1, P2, P30–P32)       27         Input ports (Ports P33, P34)       2         Output ports (Ports P52–P55)       4         12 V withstand ports       6         LED drive ports       4         Serial I/O       8-bit X 1 channel         Multi-master I <sup>2</sup> C-BUS interface       1 (2 systems)         A-D comparator (6-bit resolution)       6 channels                                                  |

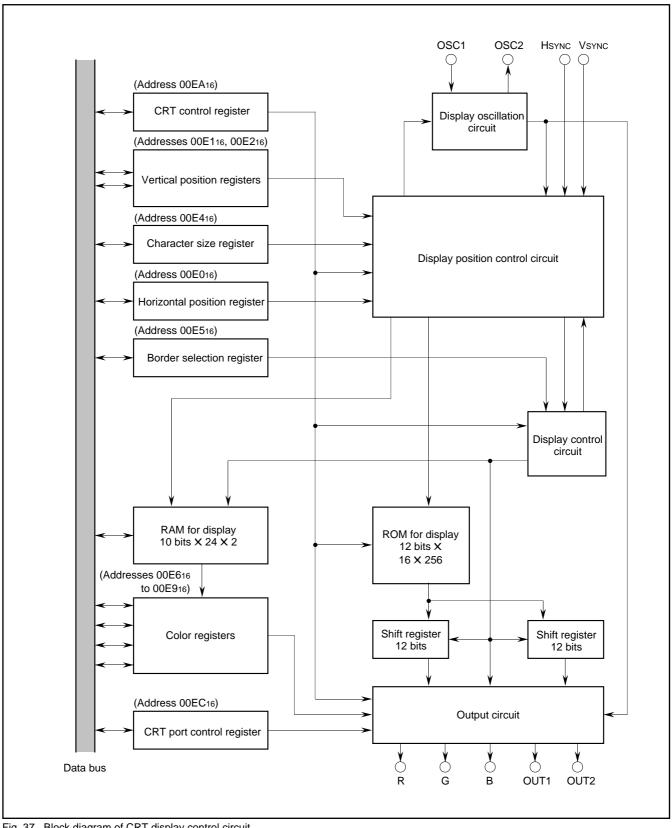

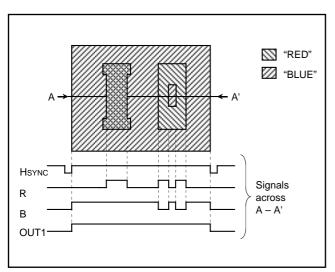

#### CRT display function

| Number of display characters 24 characters X 2 lines                        |

|-----------------------------------------------------------------------------|

| (16 lines maximum                                                           |

| Kinds of characters 256 kinds                                               |

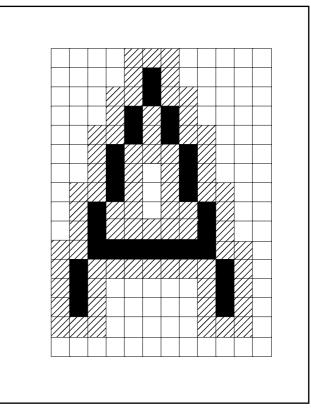

| Dot structure                                                               |

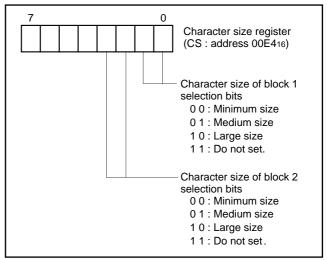

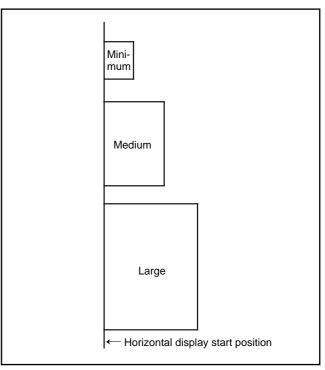

| Kinds of character sizes 3 kinds                                            |

| Kinds of character colors (It can be specified by the character)            |

| maximum 7 kinds (R, G, B)                                                   |

| Kinds of character background colors (It can be specified by the character) |

| maximum 7 kinds (R, G, B)                                                   |

| Kinds of raster colors (maximum 7 kinds)                                    |

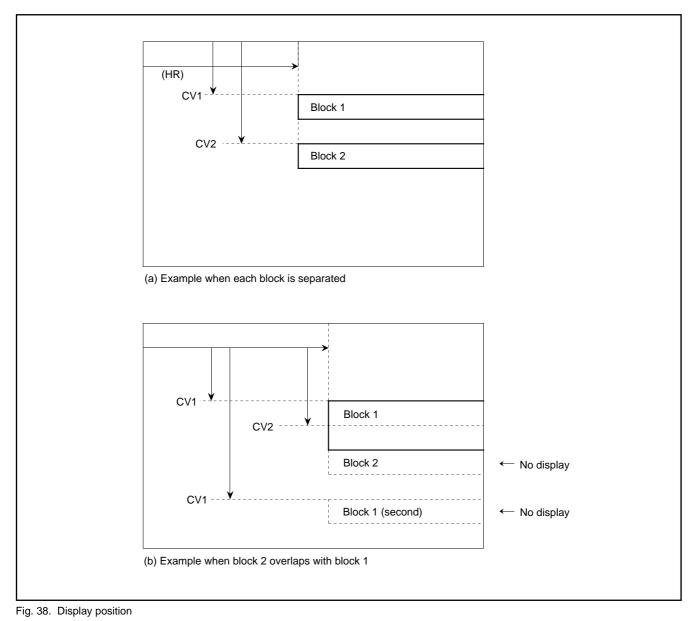

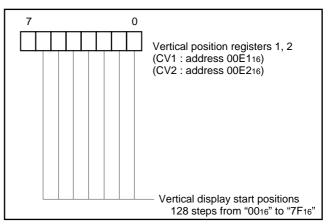

| Display position                                                            |

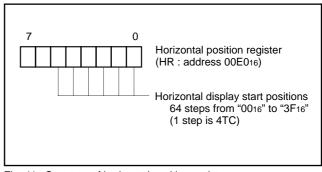

| Horizontal 64 levels                                                        |

| Vertical 128 levels                                                         |

| Bordering (horizontal and vertical)                                         |

####

## M37221EF-XXXSP,M37221EFSP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

#### **FUNCTIONS**

|                                                   | Parameter               |                   | Functions                                                                                                                                                                                                                 |  |  |  |  |  |  |

|---------------------------------------------------|-------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Number of basic instructio                        | ins                     |                   | 71                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Instruction execution time                        |                         |                   | $0.5\ \mu\text{s}$ (the minimum instruction execution time, at 8 MHz oscillation frequency)                                                                                                                               |  |  |  |  |  |  |

| Clock frequency                                   | 1                       |                   | 8 MHz (maximum)                                                                                                                                                                                                           |  |  |  |  |  |  |

| Memory size                                       | ROM                     |                   | 62 K bytes                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                                   | RAM                     |                   | 1216 bytes                                                                                                                                                                                                                |  |  |  |  |  |  |

|                                                   | CRT ROM                 |                   | 8 K bytes                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                                   | CRT RAM                 |                   | 96 bytes                                                                                                                                                                                                                  |  |  |  |  |  |  |

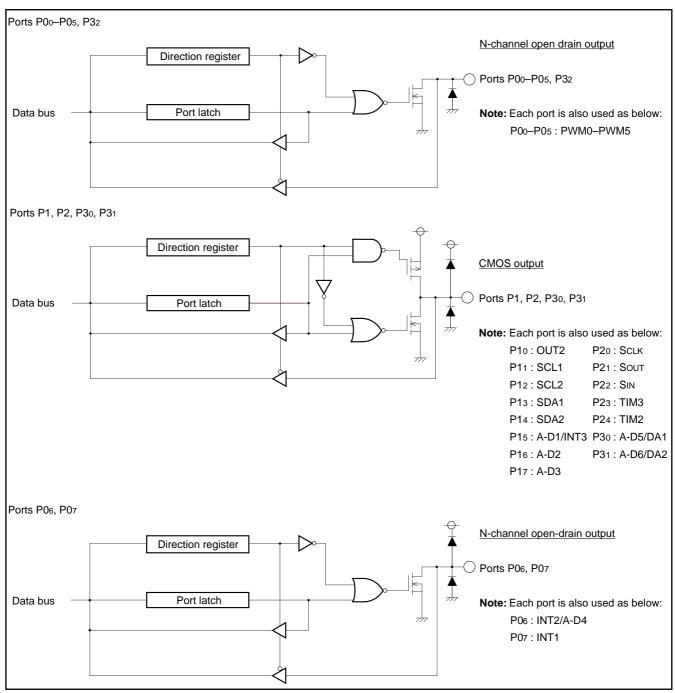

| Input/Output ports                                | P0                      | I/O               | 8-bit $\times$ 1 (N-channel open-drain output structure, can be used as PWM output pins, INT input pins, A-D input pin)                                                                                                   |  |  |  |  |  |  |

|                                                   | P10, P15–P17            | I/O               | 4-bit X 1 (CMOS input/output structure, can be used as CRT output pin, A-D input pins, INT input pin)                                                                                                                     |  |  |  |  |  |  |

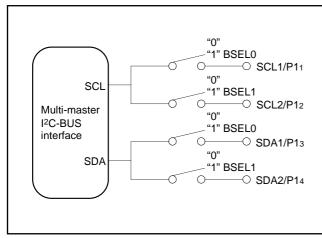

|                                                   | P11–P14                 | I/O               | 4-bit X 1 (CMOS input/output structure, can be used as multi-master l <sup>2</sup> C-BUS interface)                                                                                                                       |  |  |  |  |  |  |

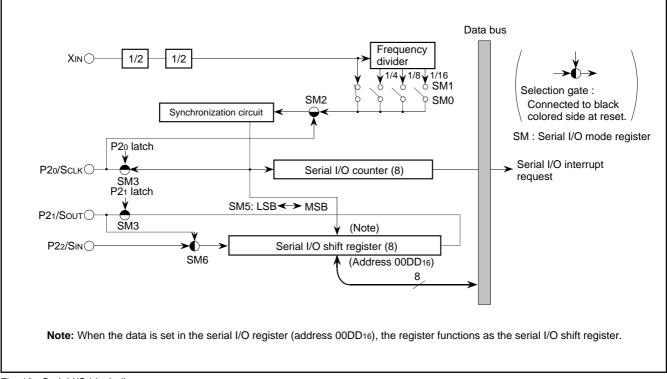

|                                                   | P20, P21                | I/O               | 2-bit X 1 (CMOS input/output or N-channel open-drain output structure, can be used as serial I/O pins)                                                                                                                    |  |  |  |  |  |  |

|                                                   | P22-P27                 | I/O               | 6-bit X 1 (CMOS input/output structure, can be used as serial input pin, external clock input pins)                                                                                                                       |  |  |  |  |  |  |

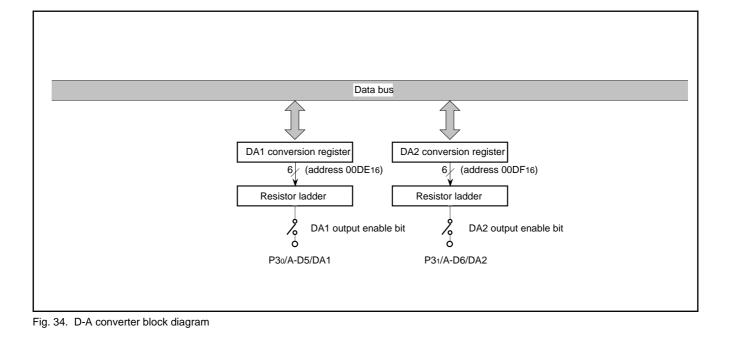

|                                                   | P30, P31                | I/O               | 2-bit X 1 (CMOS input/output or N-channel open-drain output structu<br>can be used as A-D input pins, D-A conversion output pins)                                                                                         |  |  |  |  |  |  |

|                                                   | P32                     | I/O               | 1-bit X 1 (N-channel open-drain output structure)                                                                                                                                                                         |  |  |  |  |  |  |

|                                                   | P33, P34                | Input             | 2-bit X 1 (can be used as CRT display clock I/O pins)                                                                                                                                                                     |  |  |  |  |  |  |

|                                                   | P52-P55                 | Output            | 4-bit X 1 (CMOS output structure, can be used as CRT output pins)                                                                                                                                                         |  |  |  |  |  |  |

| Serial I/O                                        |                         |                   | 8-bit X 1                                                                                                                                                                                                                 |  |  |  |  |  |  |

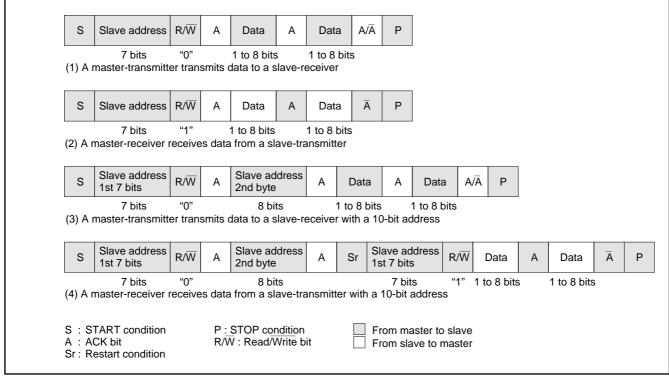

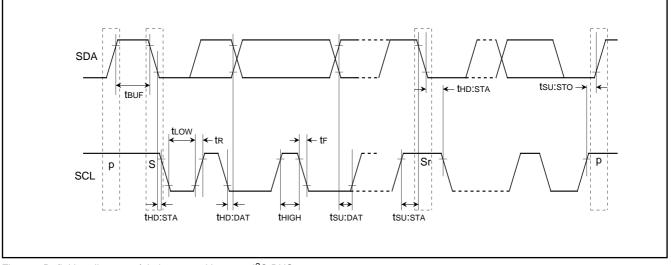

| Multi-master I <sup>2</sup> C-BUS inte            | rface                   |                   | 1 (2 systems)                                                                                                                                                                                                             |  |  |  |  |  |  |

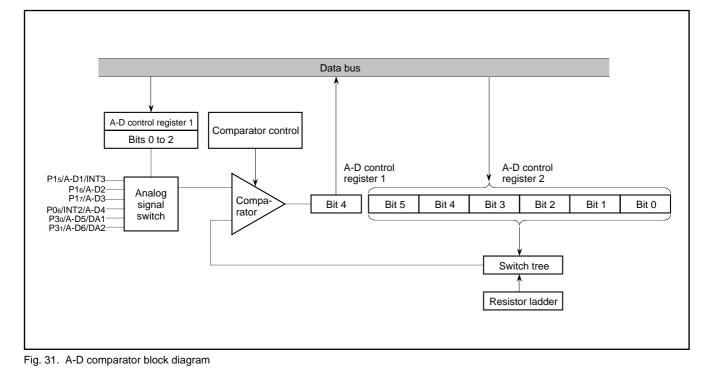

| A-D comparator                                    |                         |                   | 6 channels (6-bit resolution)                                                                                                                                                                                             |  |  |  |  |  |  |

| D-A converter                                     |                         |                   | 2 (6-bit resolution)                                                                                                                                                                                                      |  |  |  |  |  |  |

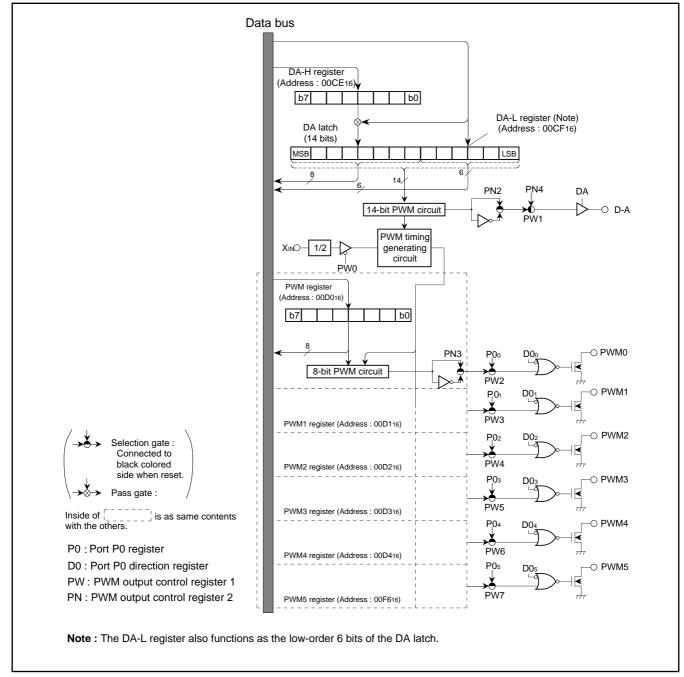

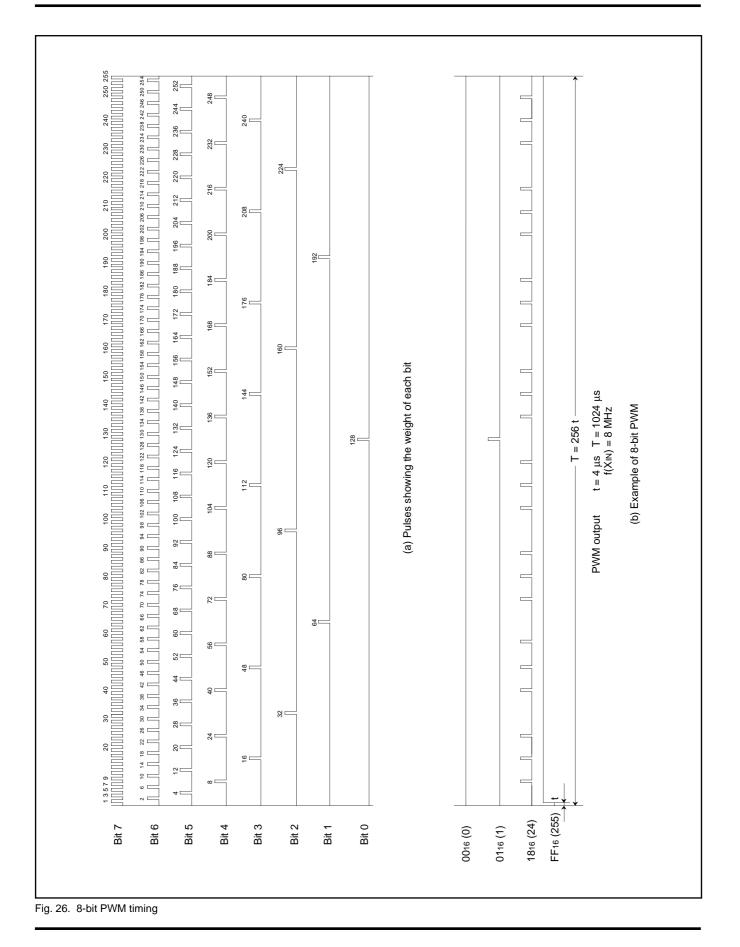

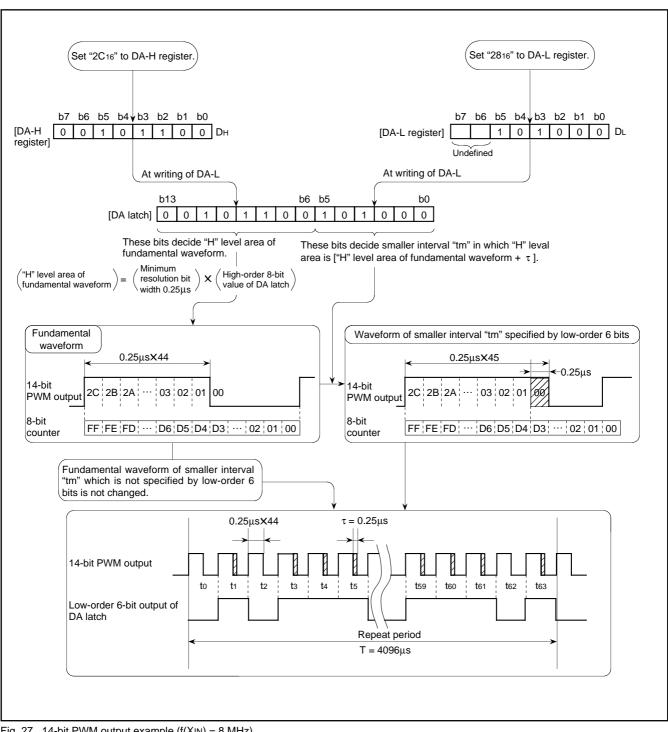

| PWM output circuit                                |                         |                   | 14-bit X 1, 8-bit X 6                                                                                                                                                                                                     |  |  |  |  |  |  |

| Timers                                            |                         |                   | 8-bit timer X 4                                                                                                                                                                                                           |  |  |  |  |  |  |

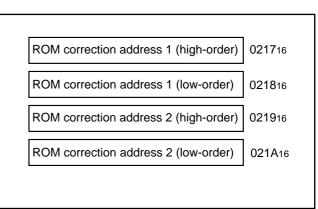

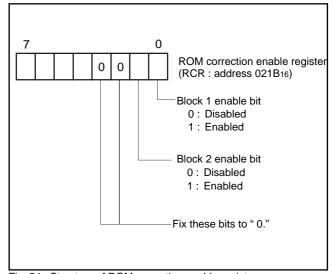

| ROM correction function                           |                         |                   | 32 bytes X 2                                                                                                                                                                                                              |  |  |  |  |  |  |

| Subroutine nesting                                |                         |                   | 96 levels (maximum)                                                                                                                                                                                                       |  |  |  |  |  |  |

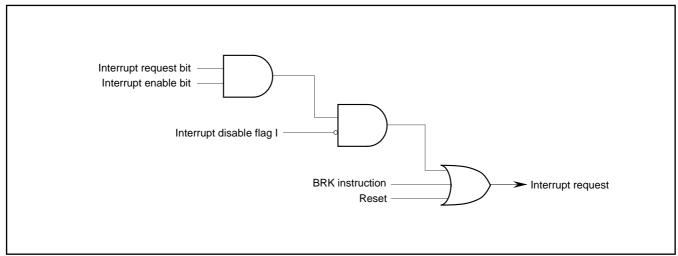

| Interrupt                                         |                         |                   | External interrupt X 3, Internal timer interrupt X 4, Serial I/O interrupt X CRT interrupt X 1, Multi-master I <sup>2</sup> C-BUS interface interrupt X f(XIN)/4096 interrupt X 1, VSYNC interrupt X 1, BRK interrupt X 1 |  |  |  |  |  |  |

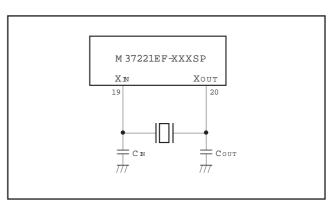

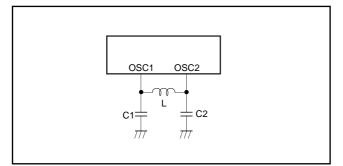

| Clock generating circuit                          |                         |                   | 2 built-in circuits (externally connected a ceramic resonator or a qua<br>crystal oscillator)                                                                                                                             |  |  |  |  |  |  |

| Power source voltage                              |                         |                   | 5 V ± 10 %                                                                                                                                                                                                                |  |  |  |  |  |  |

| Power dissipation                                 | CRT ON                  |                   | 165 mW typ. (at oscillation frequency fCPU = 8 MHz, fCRT = 8 MHz)                                                                                                                                                         |  |  |  |  |  |  |

|                                                   | CRT OFF                 |                   | 110 mW typ. (at oscillation frequency fCPU = 8 MHz)                                                                                                                                                                       |  |  |  |  |  |  |

| In stop mode                                      |                         |                   | 1.65 mW (maximum)                                                                                                                                                                                                         |  |  |  |  |  |  |

| Operating temperature ran                         | nge                     |                   | –10 °C to 70 °C                                                                                                                                                                                                           |  |  |  |  |  |  |

| Device structure                                  |                         |                   | CMOS silicon gate process                                                                                                                                                                                                 |  |  |  |  |  |  |

| Package                                           |                         |                   | 42-pin shrink plastic molded DIP                                                                                                                                                                                          |  |  |  |  |  |  |

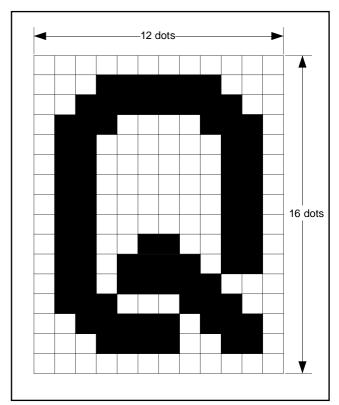

| CRT display function Number of display characters |                         | y characters      | 24 characters X 2 lines (maximum 16 lines by software)                                                                                                                                                                    |  |  |  |  |  |  |

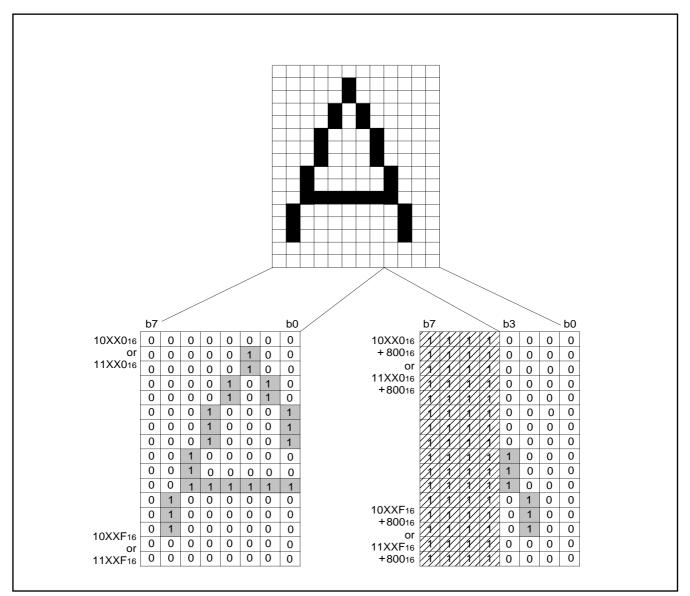

|                                                   | Dot structure           |                   | 12 X 16 dots                                                                                                                                                                                                              |  |  |  |  |  |  |

|                                                   | Kinds of characte       | rs                | 256 kinds                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                                   | Kinds of characte       | r sizes           | 3 kinds                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                                                   | Kinds of characte       | r colors          | Maximum 7 kinds (R, G, B); can be specified by the character                                                                                                                                                              |  |  |  |  |  |  |

|                                                   | Display position (horiz | contal, vertical) | 64 levels (horizontal) X 128 levels (vertical)                                                                                                                                                                            |  |  |  |  |  |  |

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

#### **PIN DESCRIPTION**

| Pin                                 | Name                                                 | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                |

|-------------------------------------|------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

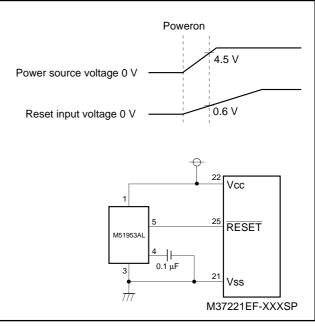

| Vcc,<br>Vss.                        | Power source                                         |                  | Apply voltage of 5 V $\pm$ 10 % (typical) to Vcc, and 0 V to Vss.                                                                                                                                                                                                                        |

| CNVss                               | CNVss                                                |                  | This is connected to Vss.                                                                                                                                                                                                                                                                |

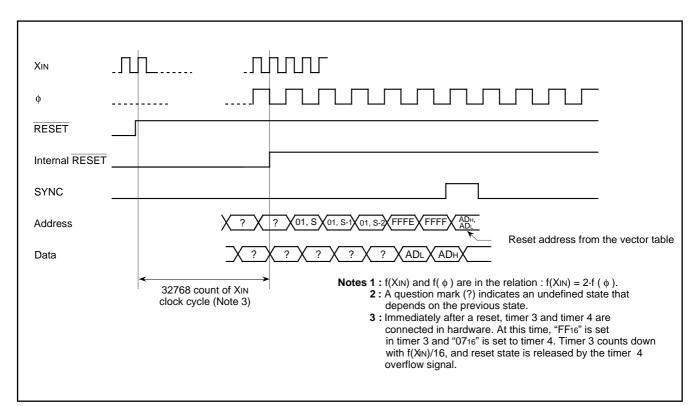

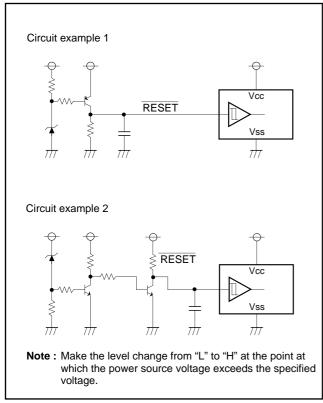

| RESET                               | Reset input                                          | Input            | To enter the reset state, the reset input pin must be kept at a "L" for 2 $\mu$ s or more (under normal Vcc conditions).<br>If more time is needed for the quartz-crystal oscillator to stabilize, this "L" condition should be maintained for the required time.                        |

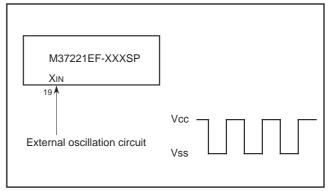

| Xin                                 | Clock input                                          | Input            | This chip has an internal clock generating circuit. To control generating frequency, an external ceramic resonator or a quartz-crystal oscillator is connected between pins XIN and                                                                                                      |

| Хоит                                | Clock output                                         | Output           | XOUT. If an external clock is used, the clock source should be connected to the XIN pin and the XOUT pin should be left open.                                                                                                                                                            |

| P00/PWM0-<br>P05/PWM5,<br>P06/INT2/ | I/O port P0                                          | I/O              | Port P0 is an 8-bit I/O port with direction register allowing each I/O bit to be individually programmed as input or output. At reset, this port is set to input mode. The output structure is N-channel open-drain output. The note out of this Table gives a full of port P0 function. |

| A-D4,<br>P07/INT1                   | PWM output                                           | Output           | Pins P00–P05 are also used as PWM output pins PWM0–PWM5 respectively. The output<br>structure is N-channel open-drain output.                                                                                                                                                            |

|                                     | External interrupt input                             | Input            | Pins P06, P07 are also used as external interrupt input pins INT2, INT1 respectively.                                                                                                                                                                                                    |

|                                     | Analog input                                         | Input            | P06 pin is also used as analog input pin A-D4.                                                                                                                                                                                                                                           |

| P10/OUT2,<br>P11/SCL1,              | I/O port P1                                          | I/O              | Port P1 is an 8-bit I/O port and has basically the same functions as port P0. The output structure is CMOS output.                                                                                                                                                                       |

| P12/SCL2,                           | CRT output                                           | Output           | Pins P10 is also used as CRT output pin OUT2. The output structure is CMOS output.                                                                                                                                                                                                       |

| P13/SDA1,<br>P14/SDA2,<br>P15/A-D1/ | Multi-master<br>I <sup>2</sup> C-BUS interface       | I/O              | Pins P11–P14 are used as SCL1, SCL2, SDA1 and SDA2 respectively, when multi-master I <sup>2</sup> C-BUS interface is used. The output structure is N-channel open-drain output.                                                                                                          |

| INT3,                               | Analog input                                         | Input            | Pins P15–P17 are also used as analog input pins A-D1 to A-D3 respectively.                                                                                                                                                                                                               |

| P16/A-D2,<br>P17/A-D3               | External interrupt input                             | Input            | P15 pin is also used as external interrupt input pin INT3.                                                                                                                                                                                                                               |

| P20/SCLK,<br>P21/SOUT,              | I/O port P2                                          | I/O              | Port P2 is an 8-bit I/O port and has basically the same functions as port P0. The output structure is CMOS output.                                                                                                                                                                       |

| P22/SIN,<br>P23/TIM3,               | External clock input                                 | Input            | Pins P23, P24 are also used as external clock input pins TIM3, TIM2 respectively.                                                                                                                                                                                                        |

| P24/TIM2,<br>P25–P27                | Serial I/O synchro-<br>nizing clock input/<br>output | I/O              | P20 pin is also used as serial I/O synchronizing clock input/output pin SCLK. The output structure is N-channel open-drain output.                                                                                                                                                       |

|                                     | Serial I/O data<br>input/output                      | I/O              | Pins P21, P22 are also used as serial I/O data input/output pins SOUT, SIN respectively. The output structure is N-channel open-drain output.                                                                                                                                            |

| P30/A-D5/<br>DA1,<br>P31/A-D6/      | I/O port P3                                          | I/O              | Ports P30–P32 are a 3-bit I/O port and has basically the same functions as port P0. Either CMOS output or N-channel open-drain output structure can be selected as the port P30 and P31. The output structure of port P32 is N-channel open-drain output.                                |

| DA2,<br>P32                         | Analog input                                         | Input            | Pins P30, P31 are also used as analog input pins A-D5, A-D6 respectively.                                                                                                                                                                                                                |

|                                     | D-A conversion<br>output                             | Output           | Pins P30, P31 are also used as D-A conversion output pins DA1, DA2 respectively.                                                                                                                                                                                                         |

| P33/OSC1,<br>P34/OSC2               | Input port P3                                        | Input            | Ports P33, P34 are a 2-bit input port.                                                                                                                                                                                                                                                   |

| 1 34/0302                           | Clock input for<br>CRT display                       | Input            | P33 pin is also used as CRT display clock input pin OSC1.                                                                                                                                                                                                                                |

|                                     | Clock output for<br>CRT display                      | Output           | P34 pin is also used as CRT display clock output pin OSC2. The output structure is CMOS output.                                                                                                                                                                                          |

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

#### **PIN DESCRIPTION (continued)**

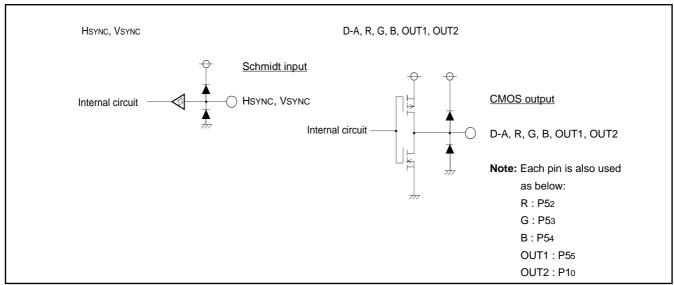

| P52/R,<br>P53/G,   | Output port P5 | Output | Ports P52-P55 are a 4-bit output port. The output structure is CMOS output.                                    |

|--------------------|----------------|--------|----------------------------------------------------------------------------------------------------------------|

| P54/B,<br>P55/OUT1 | CRT output     | Output | Pins P52–P55 are also used as CRT output pins R, G, B, OUT1 respectively. The output structure is CMOS output. |

| Hsync              | HSYNC input    | Input  | This is a horizontal synchronizing signal input for CRT.                                                       |

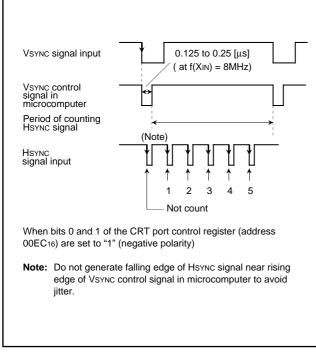

| Vsync              | Vsync input    | Input  | This is a vertical synchronizing signal input for CRT.                                                         |

| D-A                | DA output      | Output | This is a 14-bit PWM output pin.                                                                               |

Note : As shown in the memory map (Figure 3), port P0 is accessed as a memory at address 00C0<sub>16</sub> of zero page. Port P0 has the port P0 direction register (address 00C1<sub>16</sub> of zero page) which can be used to program each bit as an input ("0") or an output ("1"). The pins programmed as "1" in the direction register are output pins. When pins are programmed as "0," they are input pins. When pins are programmed as output pins, the output data are written into the port latch and then output. When data is read from the output pins, the output pin level is not read but the data of the port latch is read. This allows a previously-output value to be read correctly even if the output "L" voltage has risen, for example, because a light emitting diode was directly driven. The input pins are in the floating state, so the values of the pins can be read. When data is written into the input pin, it is written only into the port latch, while the pin remains in the floating state.

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

#### FUNCTIONAL DESCRIPTION Central Processing Unit (CPU)

The M37221EF-XXXSP uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine instructions or the SERIES 740 <Software> User's Manual for details on the instruction set.

Machine-resident 740 family instructions are as follows:

The FST, SLW instruction cannot be used.

The MUL, DIV, WIT and STP instruction can be used.

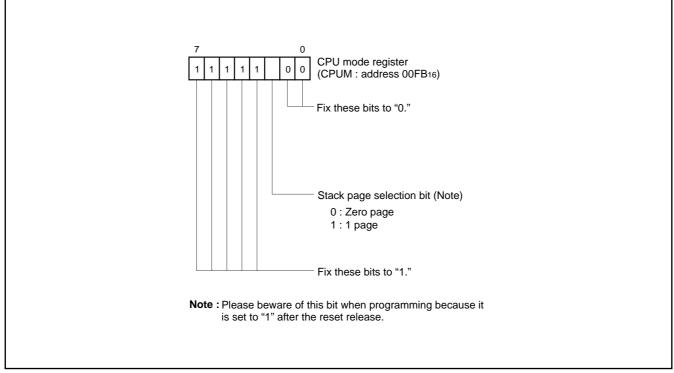

#### **CPU Mode Register**

The CPU mode register contains the stack page selection bit. The CPU mode register is allocated at address 00FB16.

Fig. 1. Structure of CPU mode register

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

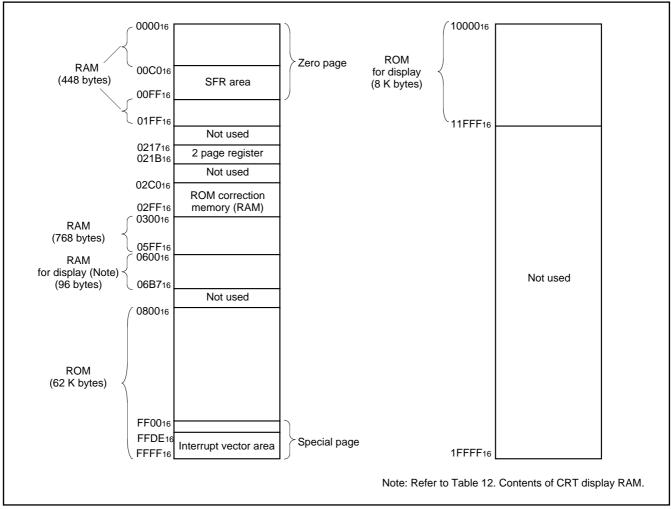

### MEMORY

#### Special Function Register (SFR) Area

The special function register ( $\overline{SFR}$ ) area in the zero page contains control registers such as I/O ports and timers.

#### RAM

RAM is used for data storage and for stack area of subroutine calls and interrupts.

#### ROM

ROM is used for storing user programs as well as the interrupt vector area.

#### **RAM for Display**

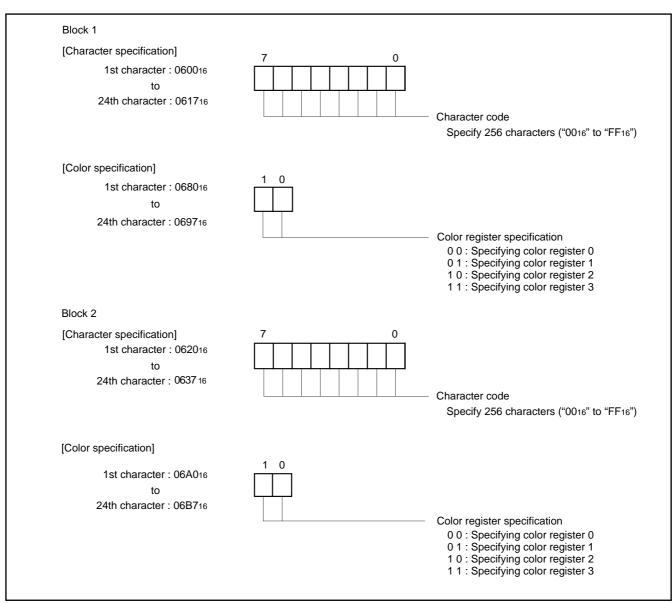

RAM for display is used for specifying the character codes and colors to display.

#### **ROM for Display**

ROM for display is used for storing character data.

#### Interrupt Vector Area

The interrupt vector area contains reset and interrupt vectors.

#### Zero Page

The 256 bytes from addresses 000016 to 00FF16 are called the zero page area. The internal RAM and the special function registers (SFR) are allocated to this area.

The zero page addressing mode can be used to specify memory and register addresses in the zero page area. Access to this area with only 2 bytes is possible in the zero page addressing mode.

#### **Special Page**

The 256 bytes from addresses FF0016 to FFFF16 are called the special page area. The special page addressing mode can be used to specify memory addresses in the special page area. Access to this area with only 2 bytes is possible in the special page addressing mode.

Fig. 2. Memory map

## M37221EF-XXXSP,M37221EFSP

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

| : Nothing is allocated                                                                           |               |            |              |        |         |       |      |      |    |      |        |             |             |      |          |          |

|--------------------------------------------------------------------------------------------------|---------------|------------|--------------|--------|---------|-------|------|------|----|------|--------|-------------|-------------|------|----------|----------|

| : Fix this bit to "0" (do not write                                                              | <b>("1</b> ") |            |              |        |         |       |      |      |    |      |        |             |             |      |          |          |

|                                                                                                  | ; ,           |            |              |        |         |       |      |      |    |      |        |             |             |      |          |          |

| 0 : "0" immediately after reset                                                                  |               |            |              |        |         |       |      |      |    |      |        |             |             |      |          |          |

| 1 : "1" immediately after reset                                                                  |               |            |              |        |         |       |      |      |    |      |        |             |             |      |          |          |

| ? : undefined immediately after r                                                                | eset          |            |              |        |         |       |      |      |    |      |        |             |             |      |          |          |

| Address Register                                                                                 |               |            | Bi           | t allo | ocatio  | on    |      |      | St | tate | imm    | edia        | atelv       | afte | r res    | set      |

| -                                                                                                | b7            |            |              |        |         |       |      | b0   |    |      |        |             |             | anto |          | k        |

| C016 Port P0 (P0)                                                                                |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| C1 <sub>16</sub> Port P0 direction register (D0)                                                 |               |            |              |        |         |       |      |      |    |      |        |             | )16         |      |          |          |

| 216 Port P1 (P1)                                                                                 |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| C3 <sub>16</sub> Port P1 direction register (D1)                                                 |               |            |              |        |         |       |      |      |    |      |        |             | <b>)</b> 16 |      |          |          |

| C416 Port P2 (P2)                                                                                |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| C516 Port P2 direction register (D2)<br>C616 Port P3 (P3)                                        |               |            |              |        |         |       |      |      | -  |      | •      |             | )16         |      |          |          |

|                                                                                                  |               |            |              |        |         |       |      |      | 0  | 0    | 0      | ?           | ?           | ?    | ?        | 1        |

| C7 <sub>16</sub> Port P3 direction register (D3)                                                 |               |            |              |        |         |       |      |      | 0  | 0    | 0      | 0           | 0           | 0    | 0        | (        |

| 2916                                                                                             |               |            |              |        |         |       |      |      |    |      |        | ?<br>?<br>? |             |      |          | _        |

| CA16 Port P5 (P5)                                                                                |               | <u> </u>   | -            |        |         | _     |      |      | 0  |      |        |             |             |      |          |          |

| B <sub>16</sub> Port P5 direction register (D5)                                                  |               |            |              |        |         |       |      |      | 0  | 0    | ?<br>0 | ?<br>0      | ?           | ?    | ?        | ?        |

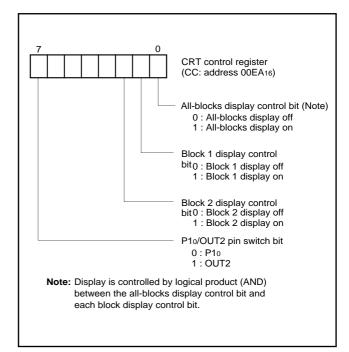

| CC16                                                                                             |               |            |              |        |         |       |      |      |    | 0    | 0      | 2           | -           | 0    | 0        |          |

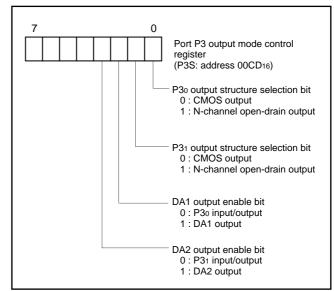

| CD16 Port P3 output mode control register (P3S)                                                  |               |            |              |        | DA2S    | DA1S  | P31S | P30S | 0  | 0    | 0      | 0           | 0           | 0    | 0        |          |

| E <sub>16</sub> DA-H register (DA-H)                                                             |               |            |              |        | 10/ 120 | 27.10 |      |      |    |      | 0      | 7           |             | 0    | 10       |          |

| F <sub>16</sub> DA-L register (DA-L)                                                             |               |            |              |        |         |       |      |      | 0  | 0    | ?      | ?           | ?           | ?    | ?        |          |

| 0016 PWM0 register (PWM0)                                                                        |               |            | -            |        |         |       |      |      |    |      | ·      | . ?         | 1           |      | <u> </u> | <u> </u> |

| 01 <sub>16</sub> PWM1 register (PWM1)                                                            |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| 216 PWM2 register (PWM2)                                                                         |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| 316 PWM3 register (PWM3)                                                                         |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| 0416 PWM4 register (PWM4)                                                                        |               |            |              |        |         |       |      |      |    |      |        | ?           | ?           |      |          |          |

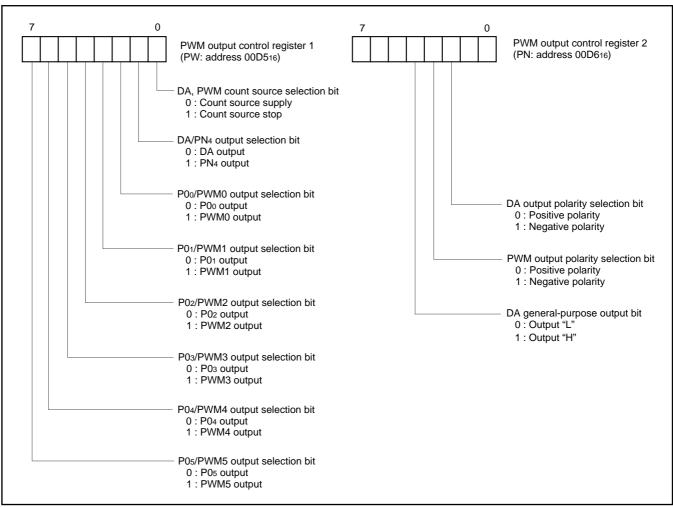

| 516 PWM output control register 1 (PW)                                                           | PW7           | PW6        | PW5          | PW4    | PW3     | PW2   | PW1  | PW0  |    |      |        | 00          | )16         |      |          |          |

| 0616 PWM output control register 2 (PN)                                                          |               |            |              | PN4    | PN3     | PN2   |      |      | 0  | 0    | 0      | 0           | 0           | 0    | 0        | (        |

| 0716 I <sup>2</sup> C data shift register (S0)                                                   |               |            |              |        |         |       |      |      |    |      |        | ?           |             |      |          |          |

| 1816 I <sup>2</sup> C address register (S0D)                                                     | SAD6          | SAD5       | SAD4         | SAD3   | SAD2    | SAD1  | SAD0 | RBW  |    |      |        | 00          | )16         |      |          |          |

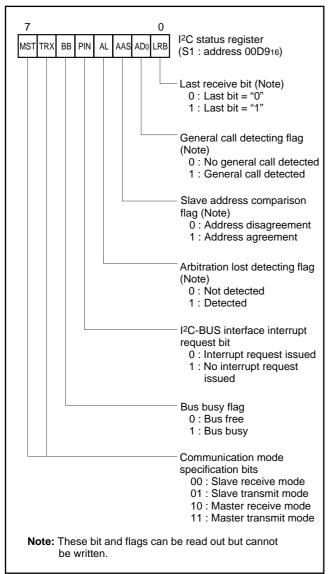

| 916 I <sup>2</sup> C status register (S1)                                                        |               | TRX        | 40 017       | PIN    | AL      | AAS   | AD0  | LRB  | 0  | 0    | 0      | 1           | 0           | 0    | 0        | 1        |

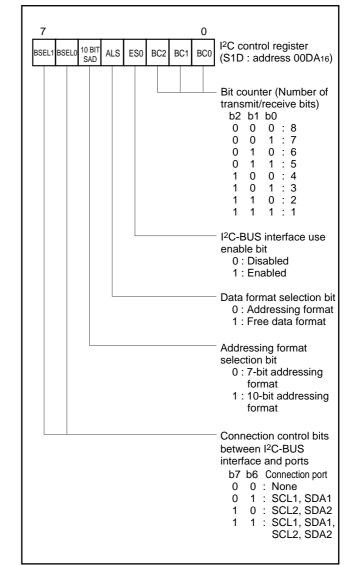

| A <sub>16</sub> I <sup>2</sup> C control register (S1D)                                          |               | BSELC      | ISAU         | ALS    | ES0     |       |      |      |    |      |        |             | )16         |      |          |          |

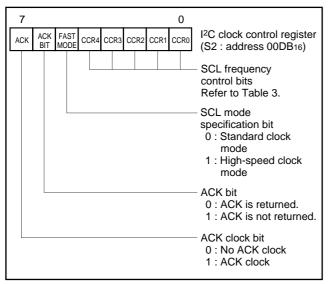

| B16 I <sup>2</sup> C clock control register (S2)                                                 | ACK           | ACK<br>BIT | FAST<br>MODE | CCR4   | CCR3    |       |      |      |    |      |        |             | )16         |      |          | 1        |

| OC <sub>16</sub> Serial I/O mode register (SM)                                                   |               | SM6        | SM5          |        | SM3     | SM2   | SM1  | SM0  | 0  | 0    | 0      | 0           | 0           | 0    | 0        | (        |

| DD <sub>16</sub> Serial I/O regsiter (SIO)                                                       |               |            | _            |        |         |       |      |      |    | 1/2/ | _      | ?           |             | -    | -        | —        |

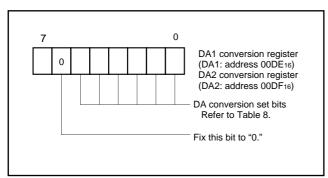

| DE <sub>16</sub> DA1 conversion register (DA1)<br>DF <sub>16</sub> DA2 conversion register (DA2) |               |            | DA15         | DA14   | DA13    | DA12  | DA11 | DA10 | 0  | 10/  | ?      | ?<br>?      | ?           | ?    | ?        | 1        |

Fig. 3. Memory map of SFR (special function register) (1)

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

| <b>—</b> .   | Nothing is allocated                                           |              | SFR area (addresses E016 to FF16) |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

|--------------|----------------------------------------------------------------|--------------|-----------------------------------|----------|--------------|--------------|--------------|----------|-------|---------------|-------|-------|-----|-----------------|-------------------|------------|---------------------|

| •            | Nothing is allocated                                           |              |                                   |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

| : []]        | Fix this bit to "0" (do not write                              | te "1        | ")                                |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

| <u></u>      | Fix this bit to "1" (do not write                              | te "0        | ")                                |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

|              | "0" immediately after reset                                    |              | ,                                 |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

|              | •                                                              |              |                                   |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

|              | "1" immediately after reset                                    |              |                                   |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

| ?:           | undefined immediately after                                    | rese         | et                                |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

|              |                                                                |              |                                   |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

|              |                                                                |              |                                   |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

| Addre        | ess Register                                                   | b7           |                                   | E        | Bit a        | lloca        | ation        |          | b0    | b7            | State | e imi | med | iatel           | y aft             | er re      | set<br>b0           |

| E016         | Horizontal register (HR)                                       |              |                                   | HR5      | HR4          | HR3          | HR2          | HR1      |       | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Vertical register 1 (CV1)                                      |              |                                   | CV15     |              |              |              |          |       | 0             | ?     | ?     | ?   | ?               | ?                 | ?          | ?                   |

|              | Vertical register 2 (CV2)                                      |              | CV26                              | CV25     | CV24         | CV23         | CV22         | CV21     | CV20  | 0             | ?     | ?     | ?   | ?               | ?                 | ?          | ?                   |

| E316         |                                                                |              |                                   |          |              |              | 1            | 1        |       |               |       | -     | 1   | r               | 1                 | 1          |                     |

|              | Character size register (CS)                                   |              |                                   |          |              | CS21         |              | CS11     |       | 0             | 0     | 0     | 0   | ?               | ?                 | ?          | ?                   |

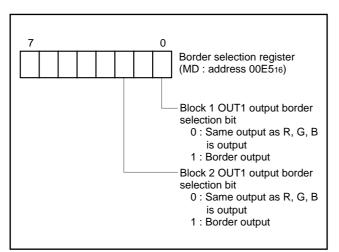

|              | Border selection register (MD)                                 |              |                                   |          |              |              | MD20         |          | MD10  | 0             | 0     | 0     | 0   | 0               | ?                 | 0          | ?                   |

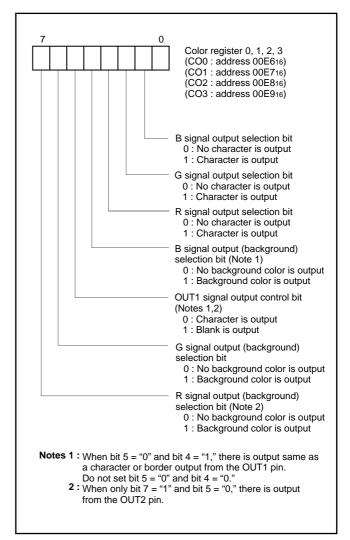

|              | Color register 0 (CO0)                                         | CO07         | CO06                              |          | CO04         | CO03         |              |          |       | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Color register 1 (CO1)                                         | CO17         | CO16                              |          | CO14         | CO13         |              | <u> </u> |       | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Color register 2 (CO2)                                         | CO27<br>CO37 | CO26<br>CO36                      |          | CO24<br>CO34 | CO23<br>CO33 | CO22<br>CO32 |          |       | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Color register 3 (CO3)<br>CRT control register (CC)            | CC7          | 0030                              | 0035     | 0034         | 0033         |              | CC1      | CC0   | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

| EB16         | CRT control register (CC)                                      |              |                                   | <u> </u> |              |              | 002          |          | 000   |               | 0     | 0     |     |                 |                   | 0          | 0                   |

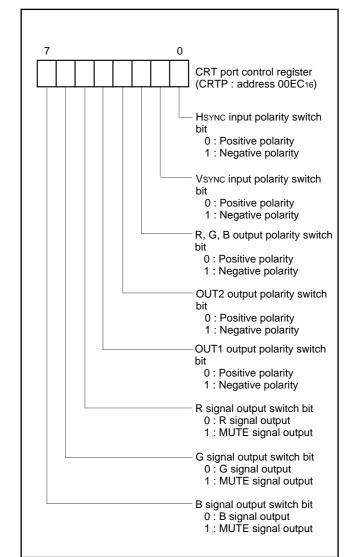

|              | CRT port control register (CRTP)                               | OP7          | OP6                               | OP5      | OUT1         | OUT2         | R/G/B        | VSYC     | HSYC  |               |       |       | 00  | -               |                   |            |                     |

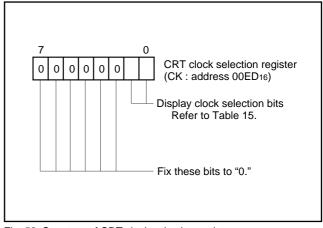

|              | CRT clock selection register (CK)                              |              |                                   |          |              |              |              | СК1      |       | 0             | 0     | 0     | NO  | 10/             | 0                 | 0          | 0                   |

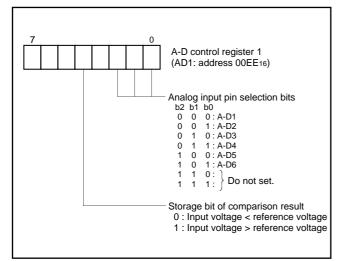

|              | A-D control register 1 (AD1)                                   |              |                                   |          | ADM4         |              | ADM2         | <u> </u> | ADM0  | 0             | 0     | 0     | ?   | 0               | 0                 | 0          | 0                   |

|              | A-D control register 2 (AD2)                                   |              |                                   | ADC5     | ADC4         | ADC3         | ADC2         | ADC1     | ADC0  | 0             | 0     | 0     | .0  | 0               | 0                 | 0          | 0                   |

| <b>F0</b> 16 | Timer 1 (TM1)                                                  |              |                                   |          |              |              |              |          |       |               |       |       | FF  | 16              |                   |            |                     |

| <b>F1</b> 16 | Timer 2 (TM2)                                                  |              |                                   |          |              |              |              |          |       |               |       |       | 07  | 7 <sub>16</sub> |                   |            |                     |

| F216         | Timer 3 (TM3)                                                  |              |                                   |          |              |              |              |          |       |               |       |       | FF  |                 |                   |            |                     |

|              | Timer 4 (TM4)                                                  |              |                                   |          |              |              |              |          |       |               |       |       | 07  | 716             |                   |            |                     |

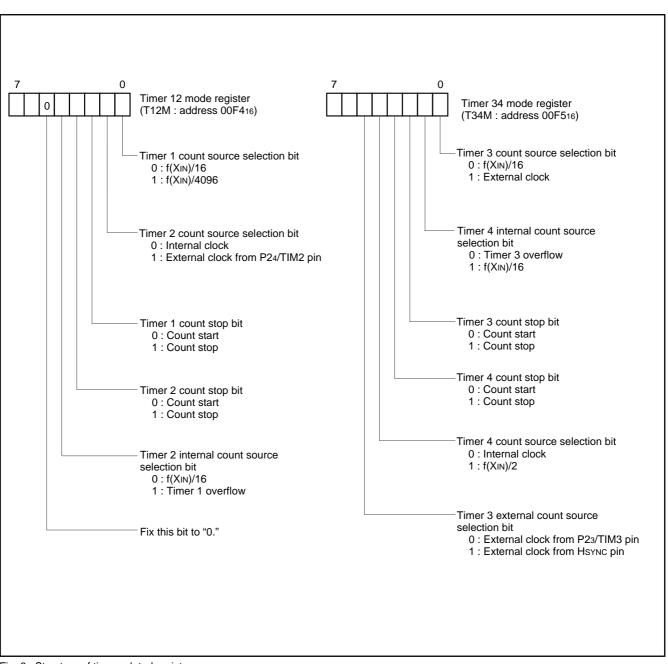

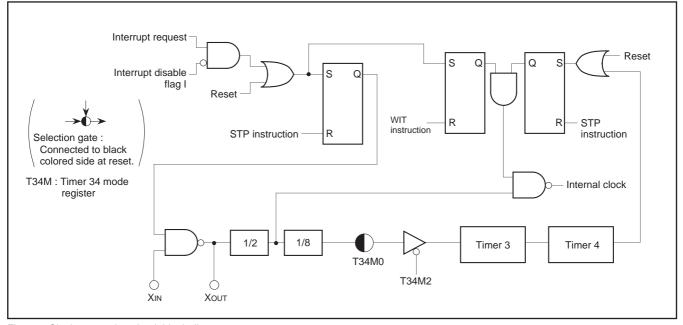

|              | Timer 12 mode register (T12M)                                  |              |                                   |          | T12M4        | T12M3        |              |          | T12M0 | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Timer 34 mode register (T34M)                                  |              |                                   | T34M5    | T34M4        | T34M3        | T34M2        | T34M1    | T34M0 | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | PWM5 register (PWM5)                                           |              |                                   |          |              |              |              |          |       |               |       |       | 1   |                 |                   |            |                     |

| F716         |                                                                |              |                                   |          |              |              |              |          |       |               |       |       |     |                 |                   |            |                     |

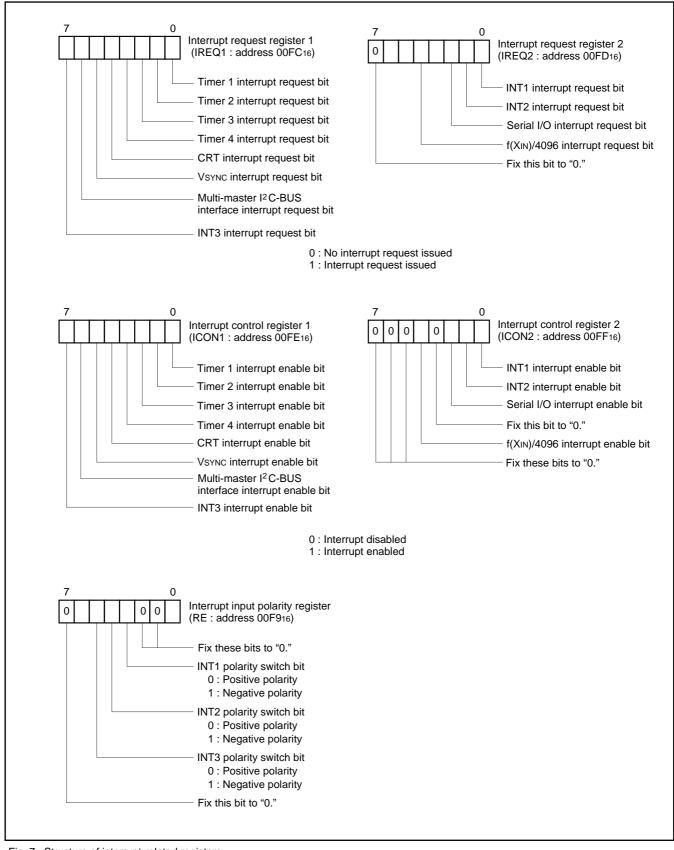

| F816         | Interrupt input polority register (DE)                         |              |                                   | DES      | RE4          | DE2          |              |          |       | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | ?                   |

|              | Interrupt input polarity register (RE)<br>Test register (TEST) |              |                                   | 11/23    |              |              |              |          |       |               |       |       |     | 1 0<br>216/1    | () <del>(</del> ( | 1 <u>0</u> | ////                |

|              | CPU mode register (CPUM)                                       |              |                                   |          |              |              | CM2          |          |       | $\rightarrow$ |       | )))   |     | X               | 1                 | 0          | $\partial \partial$ |

|              | Interrupt request register 1 (IREQ1)                           | IT3R         | IICR                              | VSCR     | CRTR         | TM4R         |              | TM2R     | TM1R  | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Interrupt request register 2 (IREQ2)                           |              |                                   |          | MSR          |              | S1R          | 1T2R     | 1T1R  | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              | Interrupt control register 1 (ICON1)                           | IT3E         | IICE                              | VSCE     | CRTE         |              |              | <u> </u> | TM1E  | 0             | 0     | 0     | 0   | 0               | 0                 | 0          | 0                   |

|              |                                                                |              |                                   |          |              |              |              |          |       |               | ~     | -     |     |                 |                   |            |                     |

Fig. 4. Memory map of SFR (special function register) (2)

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER for VOLTAGE SYNTHESIZER with ON-SCREEN DISPLAY CONTROLLER

| Address         Register         Bit allocation         State immediately after           20016         0         7         0         0         7           2016         ?         ?         ?         ?         ?           20316         ?         ?         ?         ?         ?         ?           20316         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ?         ? <td?< t<="" th=""><th></th></td?<> |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 20016       ?         20116       ?         20216       ?         20316       ?         20316       ?         20316       ?         20316       ?         20316       ?         20316       ?         20316       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         21016       ?         21116       ?         21216       ?         21316       ?         21415       ?         21516       ?         21716       ?         21716 <td< th=""><th>ter reset</th></td<>                                                                                                                                                                                                                                                                                     | ter reset |

| 20116       ?         20216       ?         20316       ?         20316       ?         20416       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20716       ?         20716       ?         20716       ?         20816       ?         20916       ?         20016       ?         20016       ?         20016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2017       ?         21316       ?         21316       ?         21316       ?         21316       ?         21316       ?         21316       ?         21316       ?         21416       ?                                                                                                                                                                                                                                                                                                                        | b0        |

| 20216       ?         20316       ?         20416       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116       ?         21116 <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                              |           |

| 20316       ?         20416       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         20516       ?         21116       ?         21116       ?         21116       ?         21116 <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                              |           |

| 20416       ?         20516       ?         20616       ?         20716       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20916       ?         20916       ?         20916       ?         20916       ?         20916       ?         20916       ?         20916       ?         20917       ?         2018       ?         2019       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?                                                                                                                                                                                                                                                                                                                        |           |

| 20516       ?         20516       ?         20716       ?         20816       ?         20816       ?         20816       ?         20816       ?         20916       ?         20816       ?         20916       ?         20016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ? <tr< td=""><td></td></tr<>                                                                                                                                                                                                                                                                                                               |           |

| 20616       ?         20716       ?         20816       ?         20916       ?         20816       ?         20916       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20816       ?         20016       ?         20016       ?         20016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         2016       ?         20116       ?         20116       ?         20116       ?         20116       ?         20116       ?         20116       ?         20116       ?         20116       ?         20116       ?                                                                                                                                                                                                                                                                                                                            |           |

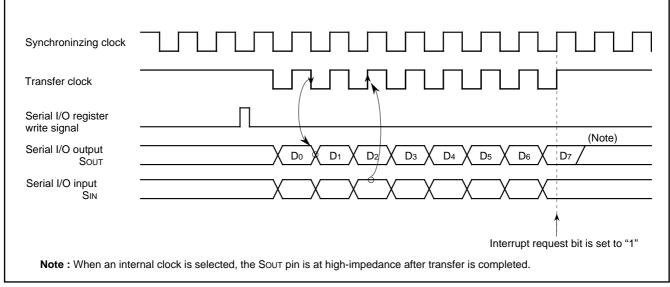

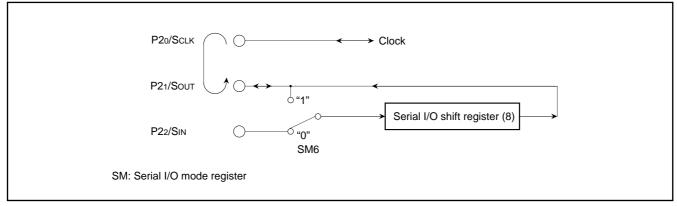

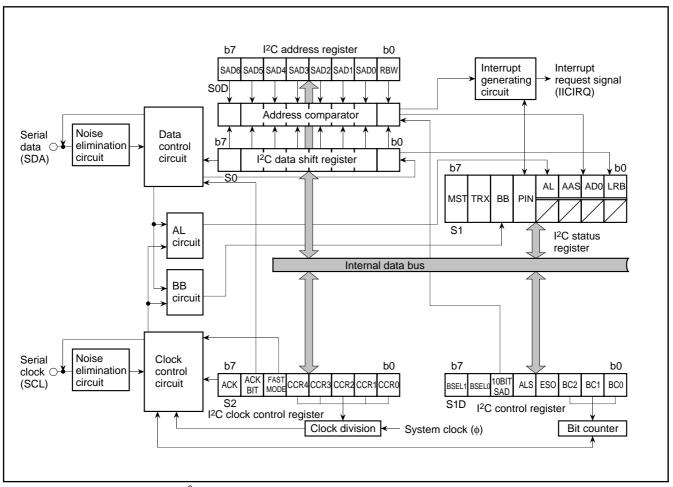

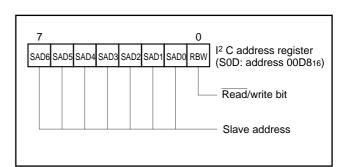

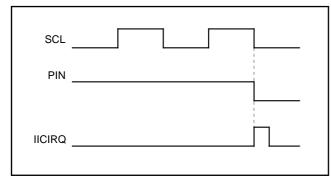

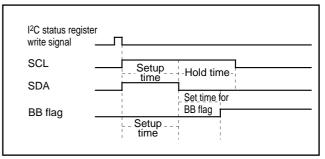

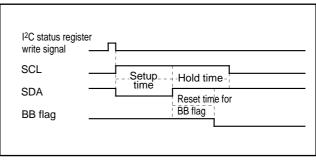

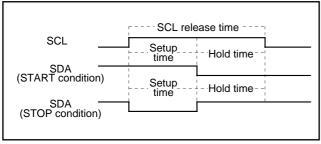

| 20716       ?         20816       ?         20916       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         200416       ?         201416       ?         201416       ?         201416       ?         201416       ?         201416       ?         201416       ?         201416       ?         201416       ?         201416       ? <tr< td=""><td></td></tr<>                                                                                                                                                                                                                                                                            |           |